PRELIMINARY

**RT10002SDH** 80V DrGaN QFN SiP Module

## Features

- Complete  $R_{DSON}$ = 2.4m $\Omega$  Half-Bridge GaN-Based power stage

- Maximum Output Current 30A.

Raytrons

- GaNCooling<sup>™</sup> technology by Bottom Side Cooling

- Low FOM for low Switching Loss at 1MHz+

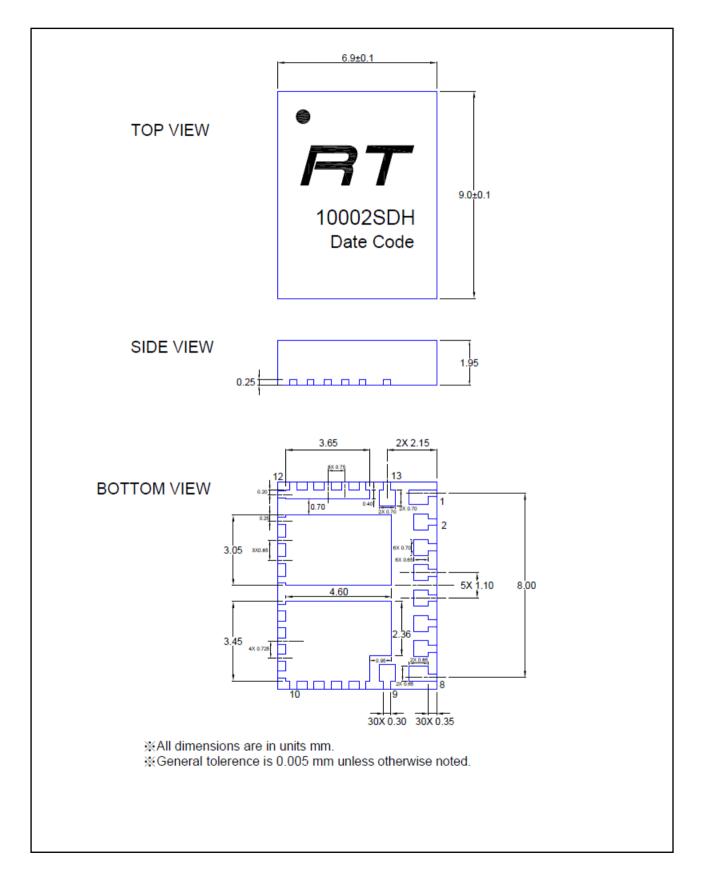

- Complete solution within 9mm x 6.9mm x 1.95mm Footprint

- Dual PWM operation

- · Fast Rise/Fall Times and low Propagation Delay

- Reverse Current capability and Zero  $Q_{\mbox{\scriptsize RR}}$

- Moisture Sensitivity Level 3 (260°C)

## **Typical Applications**

- 48V Datacenter board power delivery

- Power stage for DC-DC Converters

- 48V Mild Hybrid DC-DC Converter and BSG

- High-performance Class D Audio systems

- Motor Drive Inverter

## Description

QFN 9x6.9mm<sup>2</sup> System in Package (SiP)

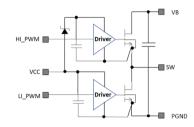

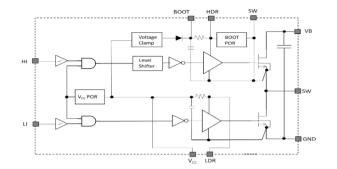

**Simplified Schematic**

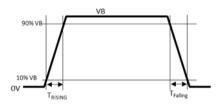

RT10 DrGaN (Driver+GaN Half Bridge) Series are Fully Integrated GaN Half-Bridge power stages for multiple Applications in Datacenter, Motor Driver, and Consumer segments. These DrGaN are small-footprint, easy-to-design, and serve as a "drop-in" solution for board power. RT10 DrGaN Series couples world-class GaN performance from EPC eGaN<sup>™</sup> to Raytrons GaNCooling<sup>™</sup> embedded modules that GaNCooling<sup>™</sup> technology is a patented construction embeds all components without using bond wires, minimizing inductance, achieving ultra-low voltage spikes on gate and switch nodes, and minimizing RFI. The high dV/dt immunity, <1nH loop inductance and low thermal resistance to provides highest level of Power Density allowing designer simple, and quick to design high power density product.

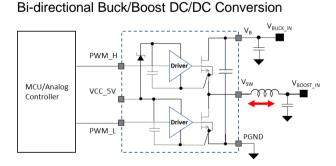

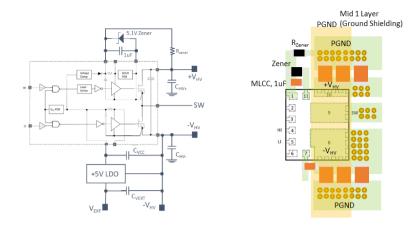

# **Typical Application Circuit**

A synchronous buck or boost topology with V<sub>CC</sub> connected to a 5-V regulated supply. Power loop (loop impedance from VB capacitor to GND) PCB layout is critical, designer can refer to the PCB layout consideration section to selection dual-loop or thermal enhanced PCB layout for various applcations

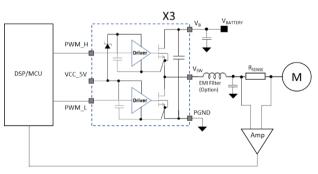

3-Phase Motor Driver

### **Block Diagram**

Raytrons

# **Pinout Table**

| Pinout  |      |                 | Description and Operation                                                                                                                            |  |  |  |

|---------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| #       | Name | I/O Type        | Description and Operation                                                                                                                            |  |  |  |

| 1       | BOOT | Supply          | Floating high side gate driver supply that connected inside                                                                                          |  |  |  |

| 2       | HDR  | -               | Option. Parallel a resistor between HDR and BST to speed up dv/dt fall time at SW node, the resistor value = $2\Omega$ is recommended if necessary.  |  |  |  |

| 4       | NC   | -               | No Connection                                                                                                                                        |  |  |  |

| 5       | HI   | Input           | Low Side PWM Input                                                                                                                                   |  |  |  |

| 6       | LI   | Input           | High side PWM Input                                                                                                                                  |  |  |  |

| 7       | LDR  | -               | Option. Parallel a resistor between LDR and VCC to speed up dv/dt rising time at SW node, the resistor value = $2\Omega$ is recommended if necessary |  |  |  |

| 8       | VCC  | Supply          | Low Side Driver Supply Voltage. Connect a 5V regulated Voltage.                                                                                      |  |  |  |

| 9,10    | GND  | Power GND       | Connect to PCB Ground thru multiple Via's                                                                                                            |  |  |  |

| 3,11,13 | SW   | Power<br>Output | Half-Bridge power stage output (switching node)                                                                                                      |  |  |  |

| 12      | VB   | Power Input     | Supply voltage to half-bridge power stage (buck-mode)                                                                                                |  |  |  |

# Absolute Maximum Ratings (T<sub>CASE</sub> = 25 °C)

Permanent device damage may occur if Absolute Maximum Ratings are exceeded.

- VB to GND, VB to SW, SW to GND ------ 85V

- VCC to GND ----- 7V

- LDR, LI, HI to GND ----- 7V

- HDR, BST to GND ----- 85V+VCC

## **Thermal Characteristics**

The Surface Mount Device (SMD) with Bottom-side Cu Pads for Surface Mount PCB attach. R\_JUNC-AMB value based on recommended Via Pattern with multi-layer FR4 PCB. No Airflow (zero LFM) and no Top-side Heat Sink required to meet R\_JUNC-AMB (Conduction Heat Transfer). It is much more effective and competitive thermal design.

- Maximum Thermal Resistance (Junction to Board), R<sub>0\_JB</sub>, ------- 1.0 °C/W

- Thermal Resistance (Junction to Ambient), R<sub>Θ\_JA</sub>, ------ 8.4 °C/W

- Maximum Soldering Temperature (MSL3 rated), T<sub>Solder</sub> ------ 260°C

| Parameter           | Sym.     | Min. | Тур. | Max. | Unit | Conditions              |

|---------------------|----------|------|------|------|------|-------------------------|

| Nominal VB Range    | VB_Nom   | 6.2  |      | 80   | V    |                         |

| Nominal SW Range    | SW_Nom   | 0.9  |      | 80   | V    |                         |

| Nominal Vcc Range   | Vcc_Nom  | 4.5  | 5    | 5.5  | V    |                         |

| Nominal I/O Voltage | VIO_Nom  |      |      | 5.5  | V    |                         |

| Continuous Iout     | IOUT_Nom |      | 25   | 30   | А    | T <sub>JUN</sub> =100°C |

| Operating Temp      | TOPER.   | -40  |      | 105  | °C   |                         |

# **Normal Operation Conditions**

Raytrons

# **Electrical Specifications**

| Parameter                       | Sym.                 | Min. | Тур. | Max. | Unit | Conditions                                                   |

|---------------------------------|----------------------|------|------|------|------|--------------------------------------------------------------|

| Drain-Source On Resistance      | R <sub>DS,ON</sub>   |      | 2.4  | 3.2  | mΩ   | H/S and L/S<br>GaN Devices                                   |

| Source-Drain Forward<br>Voltage | $V_{\text{SD}}$      |      | 1.5  |      | V    | $I_{S} = 0.5 \text{ A}, V_{GS} = 0 \text{ V}$                |

| Input Capacitance               | Ciss                 |      | 1189 | 1570 |      |                                                              |

| Reverse Transfer<br>Capacitance | Crss                 |      | 4.3  |      | pF   | $V_{\text{DS}} = 50 \text{ V},  V_{\text{GS}} = 0 \text{ V}$ |

| Output Capacitance              | Coss                 |      | 562  | 843  |      |                                                              |

| Source-Drain Recovery<br>Charge | Qrr                  |      | 0    |      | nC   |                                                              |

| Gate Resistance                 | $R_{G}$              |      | 2.2  |      | Ω    |                                                              |

| Bootstrap capacitance           | $C_{BST}$            | 80   | 220  |      | nF   | DC-Bias=0V                                                   |

| Vcc capacitance                 | Cvcc                 | 80   | 100  |      | nF   | DC-Bias=0V                                                   |

| Switching Frequency             | Fsw                  | 18   |      | 1000 | kHz  |                                                              |

| Propagation Delay               | Tpd(H,L)             |      |      | 20   | nsec | HI to SW, VB=48V,<br>VCC=5V and 10A Iout                     |

| VCC Undervoltage-Lockout        | V <sub>CC,UVLO</sub> | 3.8  | 4.0  | 4.2  | V    |                                                              |

| VCC Threshold Hysteresis        | Vcc,hys              |      | 0.35 |      | V    |                                                              |

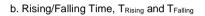

| SW Rising Time                  | Tsw,R                |      |      | 4    | nsec | VB=48V, Fsw=500kHz                                           |

| SW Falling Time                 | Tsw,F                |      |      | 6    | nsec | and 10A IOUT                                                 |

# **Application Specifications**

### VCC UVLO (Undervoltage-Lockout):

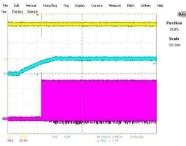

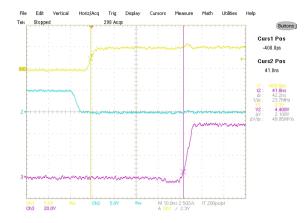

When VCC pin detects a starting threshold voltage level of 4.0V (typical) on a rising edge, the device will go from its 120uA quiescent current state to normal operation. The DrGaN will turn off after the input falls 0.35V below the starting threshold. A typical start-up waveform as below: (yellow: VB, blue: VCC and pink: SW)

### **PCB Layout Considerations :**

Raytrons

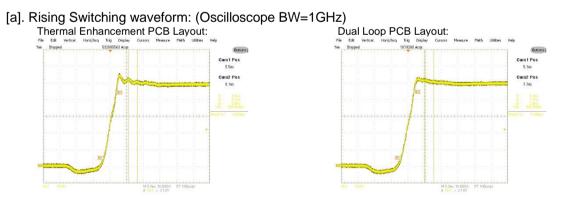

Thermal Enhanced : Utilize multiple Via's to connect PCB power and GND planes to the DrGaN Pads, designer doesn't need to consider parasitic loop inductance issue to affect high voltage spike at SW node to decrease efficiency because RT10005SDH is designed with ultra-low commutation and gate loop inductance inside. An example PCB Layout as below :

• Dual Power Loop : For further reducing power loop parasitic inductance, PCB layout can consider another PCB layout skill that is to generate a power loop with magnetic flux cancellation plus a vertical power loop inside to achieve dual power design, the power loop inductance will be reduced from <1nH to <0.5nH. That will increase efficiency and decrease voltage spike at switching node. An example PCB layout as below :

\*Mid 1 layout MUST be power ground plane.

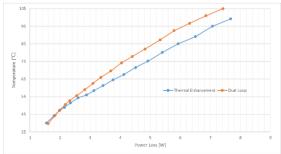

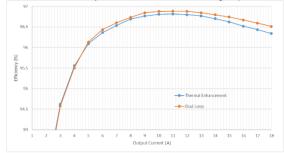

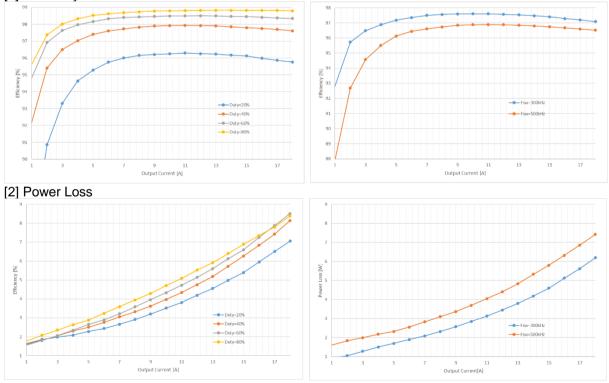

• Comparison the both PCB layout Skill : Thermal Enhancement can be handling more output current at the same environment and Dual Power Loop have better efficiency and voltage spike at SW node.

[b] Thermal performance and Efficiency between both PCB layouts Thermal Performance: Thermal enhancement PCB layout have better thermal performance because of multiple Vias on SW pad.

Efficiency: Dual Loop PCB layout have better efficiency because of smaller voltage spike at SW node.

#### Full-Bridge or 3-phase operation

Raytrons

It easily be interleaved for Full-Bridge or 3-phase operation by using MCU/DSP with multiple PWM outputs and separate control loops.

#### **Truth Table**

\*Minimum H signal is 2.3V and Maximum L signal is 0.5V.

| ні | LI | H/S GaN FET | L/S GaN FET | SW Node     |

|----|----|-------------|-------------|-------------|

| L  | L  | OFF         | OFF         | Hi-Z        |

| L  | Н  | OFF         | ON          | GND         |

| Н  | L  | ON          | OFF         | VB          |

| Н  | Н  | ON          | ON          | Not Allowed |

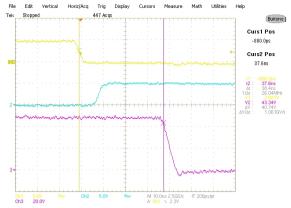

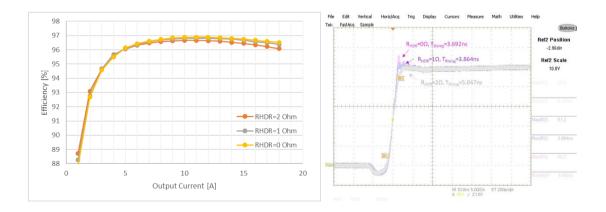

#### **Typical Efficiency and Switching Waveforms**

48V VB, Duty Cycle = 25%, F<sub>SW</sub>=500kHz, I<sub>OUT</sub> = 10A, 1GHz B.W. measurement, dead time is <15nsec, room temperature and natural convection. (All test is on the Evaluation Board)

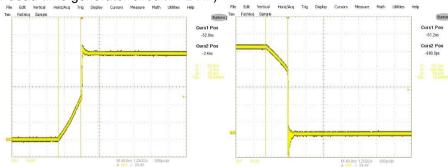

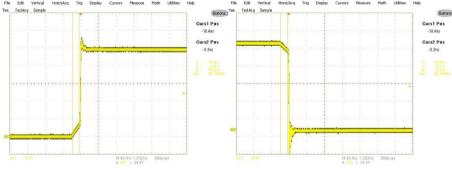

#### [3] Switching Waveforms CH1: HI (5V/DIV), CH2: LI (5V/DIV), CH3: SW (20V/DIV)

# **RT10002SDH** 80V DrGaN QFN SiP Module

aytrons

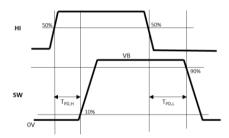

Propagation delay and rise/fall time definitions a. Propagation Delay,  $T_{\text{PD,H}}$  and  $T_{\text{PD,L}}$

### Adjustable Turn-on dV/dt Control

To reduce switching loss in high frequency hard switching operation, parallel a resistance between HDR and BST can speed up dV/dt at switching node to increase efficiency.  $R_{HDR}$  is designed =2 $\Omega$ .

$R_{HDR}$  value will change high side GaN's turned-on rising time, smaller  $R_{HDR}$  will cause faster turned-on time that will reduce switching loss, but higher voltage spike at SW node is also affect switching loss,  $R_{HDR}=2\Omega$  is recommended if needs to fine-tune efficiency.

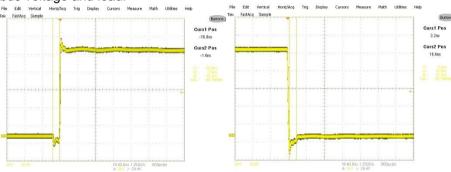

### Dead time design and operation

• Typical Delay Matching Time is 1.5ns which limits minimum Dead Time to 1.5ns, however, **at least a 15ns Dead Time is recommended** for switching reliability. Additionally, the Dual PWM DrGaN has HI and LI PWM inputs, switching control is feasible especially in ZVS Mode and in Pulse Skip or power save mode during light load operation.

In ZVS operation, controlling Dead Time low-to-high (T<sub>DT,LH</sub>) can be achieved using output inductor and the C<sub>OSS</sub> of the GaN Switch to generate a resonant period, using HI and LI to adjust T<sub>DT,LH</sub>.

Adjusting Dead Time

[1] Measure switch node to determine dead-time at no load. (Initial dead time can be set 50nsec by MCU/DSP or dead-time generator circuit in EVM)

[2] Reduce dead-time to > 15ns by MCU/DSP or dead-time generator circuit in EVM.

[3] Increase bus voltage and load.

Raytrons

### VCC Bypass Capacitor and VBST Bootstrap Capacitor

For lower switching frequency applications, likely BLDC Motor driver control, a typical switching frequency is from 20kHz to 50kHz. A 1- $\mu$ F or larger value, good-quality, ceramic bypass capacitor is recommended to place as close as possible to the VCC and GND pins for low side driver supply and to the BST and SW pins for high side floating driver supply.

### Implemented in the Class-D Amplifier Power Stage:

Due to GaN FET has much smaller  $Q_G$  and  $C_{OSS}$  than MOSFET that will produce a much more accurate PWM replication of the large output signal to increase sound quality in Class-D audio system. An example for half bridge Class-D audio amplifier schematic and recommended PCB layout are shown as below:

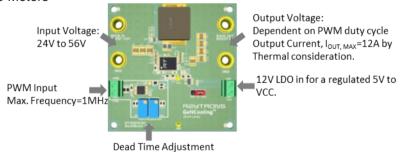

### 48V to 12V Open Loop Buck/Boost Evaluation Board:

Raytrons

The Evaluation Board with 100V DrGaN SMT power stage provides a complete 48V step Up/down converter which can be used to evaluate efficiency & power density for use in applications such as DC/DC Converter power stage, high-performance Class D audio systems, and BLDC Motor Driver.

To evaluate the performance of the evaluation board, the following equipment is required:

- · High speed digital oscilloscope (350MHz Bandwidth at least)

- DC load (power resistor or electrical load)

- DC power supplies \*2 (For power in and VCC in)

- Signal generator for PWM input (0-5V)

- Current/Voltage Meters

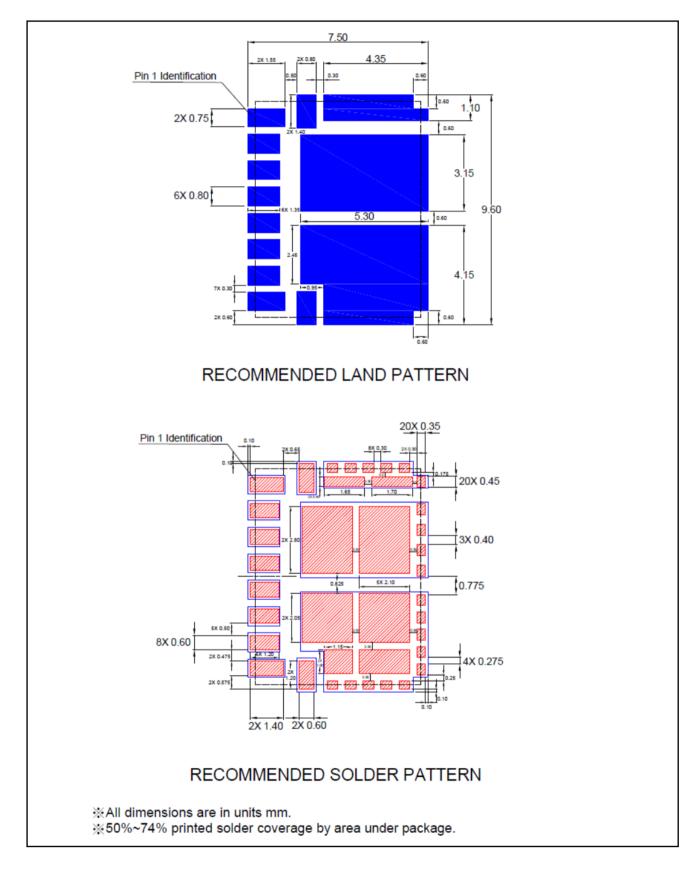

## Package Outline : (QFN-SiP - 2 mm max height)

Raytrons

### Example Board Layout and Stencil Design :